在全球半导体产业向更精密制程迈进的背景下,日本大日本印刷株式会社(DNP)近日宣布突破性成果:成功研发出线宽仅10纳米的纳米压印(NIL)光刻模板,该技术可实现相当于1.4纳米级逻辑半导体的图形化加工,为智能手机、数据中心及NAND闪存等设备的芯片微型化提供新方案。这项成果将于2025年12月17日至19日在东京国际展览中心举办的日本国际半导体展(SEMICON Japan 2025)上首次公开亮相。

随着人工智能、5G等新兴技术对算力需求的爆发式增长,半导体行业正面临双重挑战:一方面需要持续推进制程微缩,另一方面需应对EUV光刻技术带来的高昂成本。目前主流的极紫外(EUV)光刻设备单价高达1.5亿美元,其生产线的建设与运营成本居高不下,且曝光环节的能耗问题日益凸显。在此背景下,日本厂商佳能自2013年起与DNP展开深度合作,共同探索纳米压印技术的产业化路径。

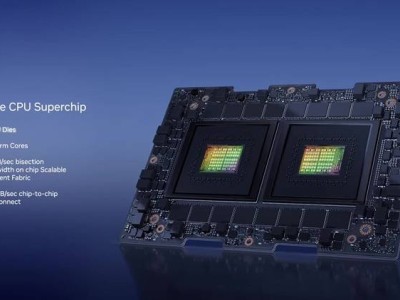

与传统光学投影式光刻不同,纳米压印技术采用类似印刷的物理压印方式,通过单次压印即可在晶圆表面形成复杂2D/3D电路结构。佳能2023年推出的FPA-1200NZ2C设备已验证该技术可支持5纳米制程,且设备采购成本较EUV光刻机降低90%,制造环节能耗更可减少约九成。佳能首席执行官御手洗富士夫曾公开表示,其纳米压印设备价格将控制在ASML EUV光刻机的十分之一水平。

技术突破的关键在于模板制造精度。DNP采用的自对准双重图案化(SADP)技术,通过薄膜沉积与蚀刻工艺使图案密度翻倍,最终实现10纳米线宽的突破。这项成果意味着纳米压印技术可替代部分EUV工艺,甚至在特定场景下取代更先进的High NA EUV设备。据技术文档显示,该模板采用1:1尺寸传递模式,虽在20纳米以下制程需依赖多光束电子束写入机(MBMW)支持,但已显著降低缺陷率与制造成本。

在环保与经济性双重驱动下,DNP的解决方案正获得行业关注。其开发的超精细半导体工艺可将功耗降至传统ArF/浸没式DUV及EUV工艺的十分之一。目前该公司已启动客户评估流程,计划于2027年实现量产,并设定2030财年NIL业务销售额增长40亿日元的目标。业内分析认为,当制程推进至埃米级时,纳米压印技术的成本优势将进一步放大,可能重塑高端半导体制造格局。

这项突破的背后是DNP长达二十年的技术积累。自2003年启动NIL模板研发以来,该公司通过直接压印转移电路图案的技术路线,逐步构建起独特的技术壁垒。此次10纳米线宽模板的诞生,不仅验证了物理压印方式在先进制程的可行性,更为半导体产业提供了除EUV之外的第二条技术路径选择。随着全球主要经济体对芯片自主可控的需求上升,纳米压印技术有望在特定领域形成差异化竞争优势。