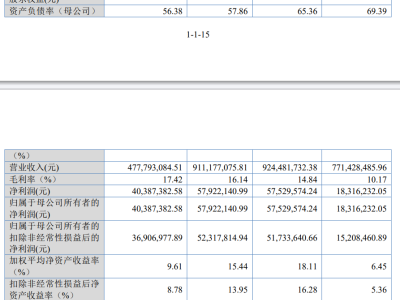

半导体行业近日迎来新动态,英特尔“Panther Lake-H”移动端处理器的内部结构通过深度分析平台Kurnal Insights发布的裸片图首次公开。这款处理器延续了分离式芯片设计理念,整体布局与前代Arrow Lake-H和Meteor Lake存在相似性,但核心模块的排列方式更接近Lunar Lake架构。其核心由四个功能模块组成,通过基底模块实现物理堆叠与电气连接,最终形成规整的矩形结构。

作为处理器的基础支撑,基底模块采用22纳米工艺制造,承担着中介层的角色。该模块通过高密度布线为上层三个计算模块提供电气连接,确保Compute Tile、Graphics Tile和I/O Tile能够紧密协同工作。英特尔通过填充硅块(Filler Tile)技术,巧妙解决了不规则堆叠导致的外形问题,使芯片最终呈现标准化矩形外观。

Compute Tile是处理器的运算核心,尺寸达14.32×8.04毫米,总面积约115平方毫米。该模块采用6P+8E+4LPE的混合架构设计,包含6个Cougar Cove性能核心与2个Darkmont效率核心,通过Ringbus环形总线实现18MB共享L3缓存的互联。性能核心配备3MB独立L2缓存,效率核心组则共享4MB L2缓存。在频率表现上,性能核心最高可达5.10GHz,效率核心最高运行频率为3.80GHz,低功耗独立核心的基础频率更低但最高仍可达3.70GHz。

内存子系统方面,Compute Tile集成了双通道内存控制器,支持DDR5和LPDDR5X两种内存标准,最高数据传输速率达9600MT/s。模块内还配备8MB内存侧缓存,有效降低内存访问延迟。第五代神经网络处理单元(NPU 5)同样位于该模块,其包含三个神经计算引擎,每个引擎配备1.5MB专用缓存,总缓存容量达4.5MB,剩余晶体管资源则分配给媒体编解码等辅助功能。

Graphics Tile专注于图形处理,尺寸为8.14×6.78毫米,面积约55.18平方毫米。该模块基于Xe3 Celestial架构,集成12个Xe图形核心和16MB L2缓存。值得注意的是,在主流型号中该模块采用Intel 3工艺制造,仅包含4个Xe核心,而面向轻薄本市场的Panther Lake-U处理器则配备采用台积电N3E工艺的12核心版本,显示英特尔在不同产品线上的工艺策略差异。

I/O Tile负责处理器的对外连接功能,尺寸为12.44×4毫米,面积约49.76平方毫米。该模块集成PCIe根集线器,提供4条PCIe 5.0和8条PCIe 4.0通道,满足高速存储和外设扩展需求。雷电5控制器(兼容USB4 v2规范)可提供2个40Gbps接口,无线连接模块则支持Wi-Fi 7和蓝牙5.4标准,构成完整的现代计算设备连接方案。

裸片图作为芯片设计的关键分析工具,通过显微摄影技术清晰呈现处理器各模块的物理布局与面积占比。这种技术手段不仅帮助行业观察者理解芯片架构设计思路,也为评估制造工艺水平、计算模块效率等关键指标提供直观依据。英特尔此次通过模块化设计,在单一处理器中整合了三种不同制程工艺,这种异构集成策略或将成为未来高端移动处理器的发展方向。