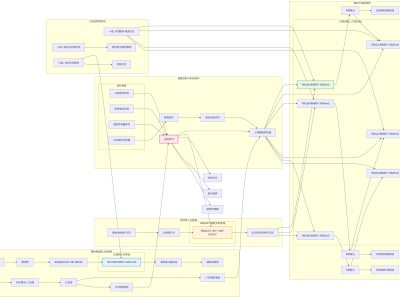

在财报电话会议上,台积电董事长魏哲家就公司封装技术与英特尔EMIB方案的竞争态势作出回应。他表示,凭借最大光罩尺寸封装方案与SoIC技术的协同优势,台积电有信心为客户提供更具竞争力的封装选择。这一表态凸显了台积电在先进封装领域的战略定力。

作为当前主力封装方案,CoWoS的产能扩张计划已明确落地。根据供应链披露的数据,该技术月产能将于2026年底突破11.5万片晶圆,2027年进一步增至约17万片。为应对AI芯片市场爆发式需求,台积电正加速台南、嘉义两地的产线建设,通过扩大生产规模巩固市场地位。

面向未来技术布局,台积电已启动CoPoS面板级封装研发项目。据悉,位于新竹的试点产线于今年2月完成核心设备安装,预计6月实现全线贯通。市场分析机构预测,这项突破传统封装尺寸限制的技术最早将于2028至2029年进入量产阶段,后续应用规模将逐步扩大。

CoPoS的技术突破性体现在采用面板级工艺,通过扩大封装基板面积显著提升单位产出效率,同时有效降低制造成本。这种特性使其成为AI专用集成电路(ASIC)和图形处理器(GPU)等大尺寸芯片的理想解决方案,有望重塑超大规模芯片封装的市场格局。

在市场竞争层面,台积电现有封装方案已形成显著生态优势。英伟达H100、A100等主流AI加速器均采用CoWoS封装,构建起完整的技术供应链体系。而即将量产的CoPoS技术将通过支持更高带宽和更大集成规模,进一步强化台积电在超大尺寸封装领域的技术壁垒,形成对竞争对手的差异化优势。