混合键合技术作为半导体制造领域的核心突破,正在推动芯片堆叠密度向亚微米级迈进。当前主流工艺已实现8至6微米间距的量产,但下一代人工智能与高性能计算设备对功率效率和集成度的需求,迫使行业向5微米以下间距发起挑战。这一技术跃迁不仅要求工艺窗口压缩至双位数纳米级,更引发了从材料处理到设备集成的系统性变革。

泛林集团高级副总裁瓦希德·瓦赫迪在ITF World技术论坛上指出,当键合间距缩小至亚微米范围时,工艺变量呈现指数级增长。现代键合设备虽具备10至18个独立参数调节旋钮,但工程师在海量组合中寻找最优解的难度堪比"大海捞针"。这种复杂性倒逼行业重构设计-计量-制造的交互模式,将人工智能驱动的虚拟制造纳入核心流程。

表面形貌控制成为突破亚微米键合的关键战场。imec公司演示的700纳米金属间距晶圆键合显示,化学机械抛光(CMP)产生的2纳米级凹陷即可导致接触电阻激增。Brewer Science技术专家道格拉斯·格雷罗强调,晶圆接触前的表面处理精度必须达到分子级,任何有机污染物或颗粒残留都会引发键合界面空洞。这种严苛要求推动清洁工艺向"预防优于修复"模式转变,集成在线形貌监测的CMP设备已成为新标配。

热机械变形管理构成另一重技术壁垒。西门子EDA产品总监约翰·弗格森分析指出,当晶圆厚度降至50微米以下时,临时键合/解键合过程产生的0.1微米级翘曲就会破坏键合对准。imec研发副总裁朱利安·里卡特透露,行业正通过低温键合工艺和实时变形补偿算法应对挑战,某些先进设备已能将热膨胀误差控制在0.3微米以内。

缺陷检测体系面临全面升级。Microtronic应用总监埃罗尔·阿科默发现,传统微观缺陷检查已不足以保障亚微米键合良率,晶圆边缘0.5毫米范围内的碎裂和胶带残留正成为主要失效源。这促使行业将宏观形貌检测纳入质量控制体系,通过边缘场检测技术实现全晶圆覆盖监控。

晶圆到晶圆(W2W)与芯片到晶圆(C2W)的技术路线之争愈发激烈。美光科技执行副总裁斯科特·德博尔认为,虽然C2W通过已知良好芯片组装提升了初始良率,但W2W在热管理和批量生产效率方面更具潜力。这种选择正推动键合设备向集群化发展,EV Group最新机型已实现50纳米对准精度,结合扫描器网格测量技术可将重复性控制在0.6纳米以内。

制造生态系统的重构催生出新型协作模式。Synopsys产品总监阿姆伦杜·乔贝指出,传统的设计-制造分离模式在亚微米时代难以为继,组装设计套件(ADK)正将制造约束转化为可执行的设计规则。这些规则不仅涵盖几何间距,还延伸至热预算、材料组合等工艺参数,形成覆盖整个堆栈的签核体系。

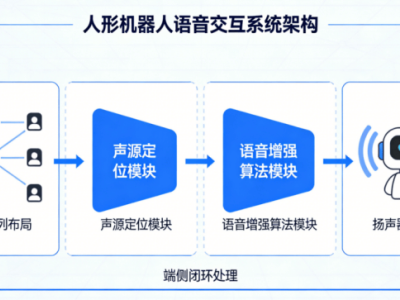

实时反馈控制系统成为保障量产稳定性的核心。拉姆研究开发的智能校正回路,通过集成对准传感器、热漂移监测器和键合力计,实现了工艺参数的动态调整。这种闭环控制与人工智能预测模型相结合,可将工艺漂移抑制在0.1微米/小时以内,显著提升长时间运行的良率稳定性。

尽管技术突破不断涌现,亚微米混合键合的规模化生产仍面临多重挑战。设备互操作性问题在ECTC会议上引发关注,多数成功案例依赖于单一供应商的集群化方案,而实际生产环境中的异构设备集成仍存在调度和环境控制难题。材料兼容性则是另一大障碍,不同代工厂芯片的金属化工艺差异可能导致键合界面失效。

在这场技术竞赛中,工艺窗口的收窄与经济性的平衡成为决定胜负的关键。行业数据显示,键合周期每增加1秒虽能提升0.2%的良率,但会导致生产线产能下降3%。这种矛盾迫使制造商采用虚拟制造技术缩小实验范围,通过迁移学习算法加速工艺开发,在保证质量的同时控制生产成本。