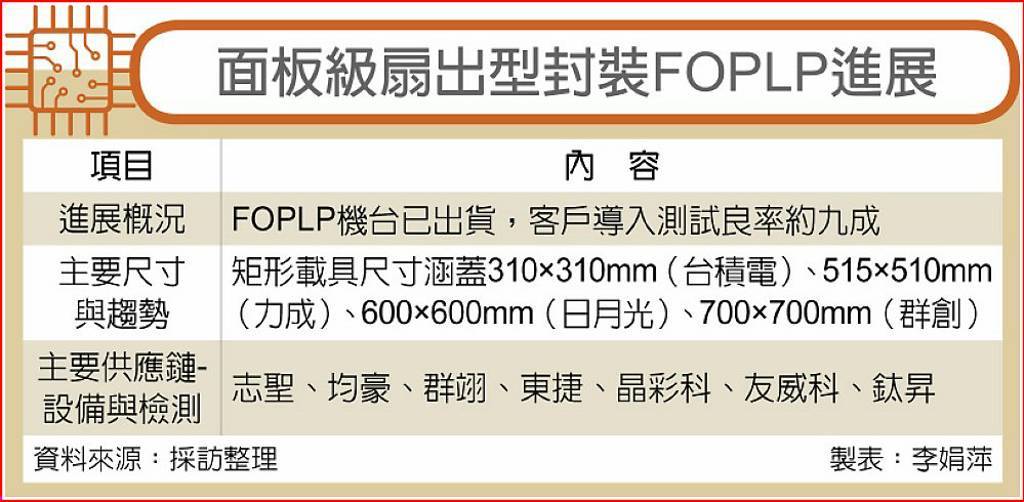

半导体封装领域正迎来技术革新,面板级扇出封装(FOPLP)成为行业焦点。这项由台积电等厂商主导研发的新型封装技术,通过将传统晶圆载板替换为矩形面板,实现了成本与效率的双重突破。据供应链消息,FOPLP设备已进入客户测试阶段,首批试产良率达90%,但大尺寸应用仍需突破量产瓶颈。

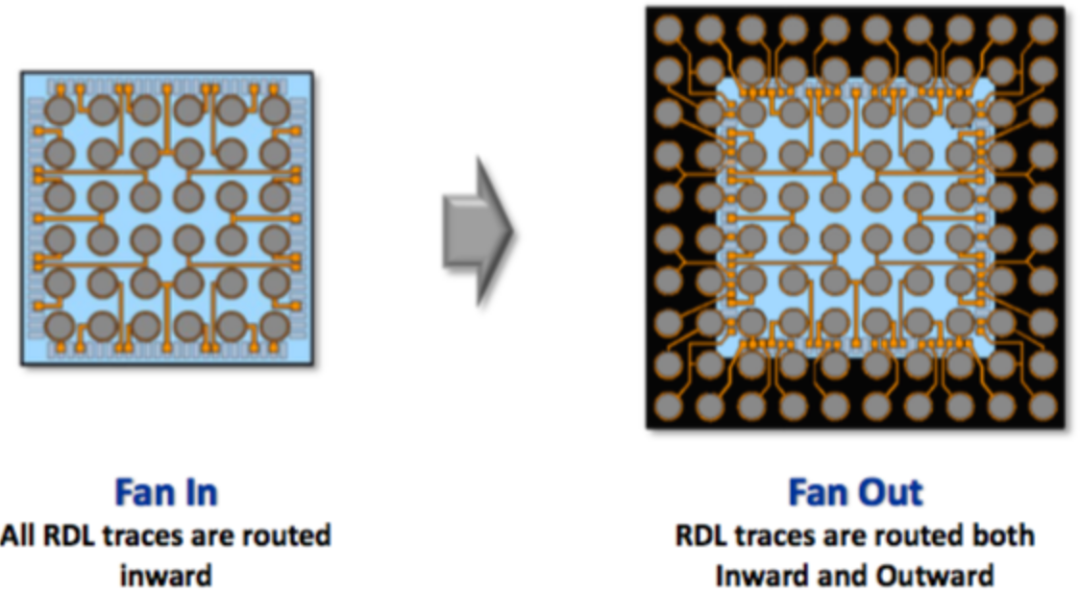

FOPLP的核心优势在于载板形态的革新。相较于传统晶圆级扇出封装(FOWLP)采用的圆形载板,FOPLP使用600×600毫米的方形面板,面积超过12英寸晶圆的五倍。这种设计使材料利用率从57%提升至87%,显著降低了单位封装成本。技术原理上,该技术通过在芯片投影面积外围扩展导线重新分布层(RDL),突破了扇入型封装的空间限制。

行业推进呈现双轨并行态势。群创光电与力成科技已实现小规模量产,主要应用于电源管理芯片等中小型器件封装。其中力成科技部署新一代激光与点胶设备后,试产良率突破90%,预计明年可达95%以上。另一条技术路径由台积电主导,其开发的CoPoS(晶圆级面板封装)方案瞄准英伟达、AMD等厂商的高性能GPU需求,目前试产阶段仍面临技术瓶颈。

载板材料与尺寸标准逐步确立。当前主流方案包括台积电310×310毫米、力成515×510毫米、日月光600×600毫米及群创700×700毫米四种规格,材质以金属和玻璃为主。台积电特别投资TGV(穿玻璃通孔)技术推动玻璃基板发展,其专属研发团队已建立完整产线,原定2027年的量产计划可能提前实施。

产能调整伴随技术升级同步进行。台积电今年8月宣布将在两年内淘汰6英寸晶圆产线,并整合8英寸产能。晶圆二厂(6英寸)与五厂(8英寸)的改造方向尚未确定,但业界猜测可能转型为CoPoS专用产线。这一系列布局显示,先进封装技术正成为半导体厂商竞争的新战场。