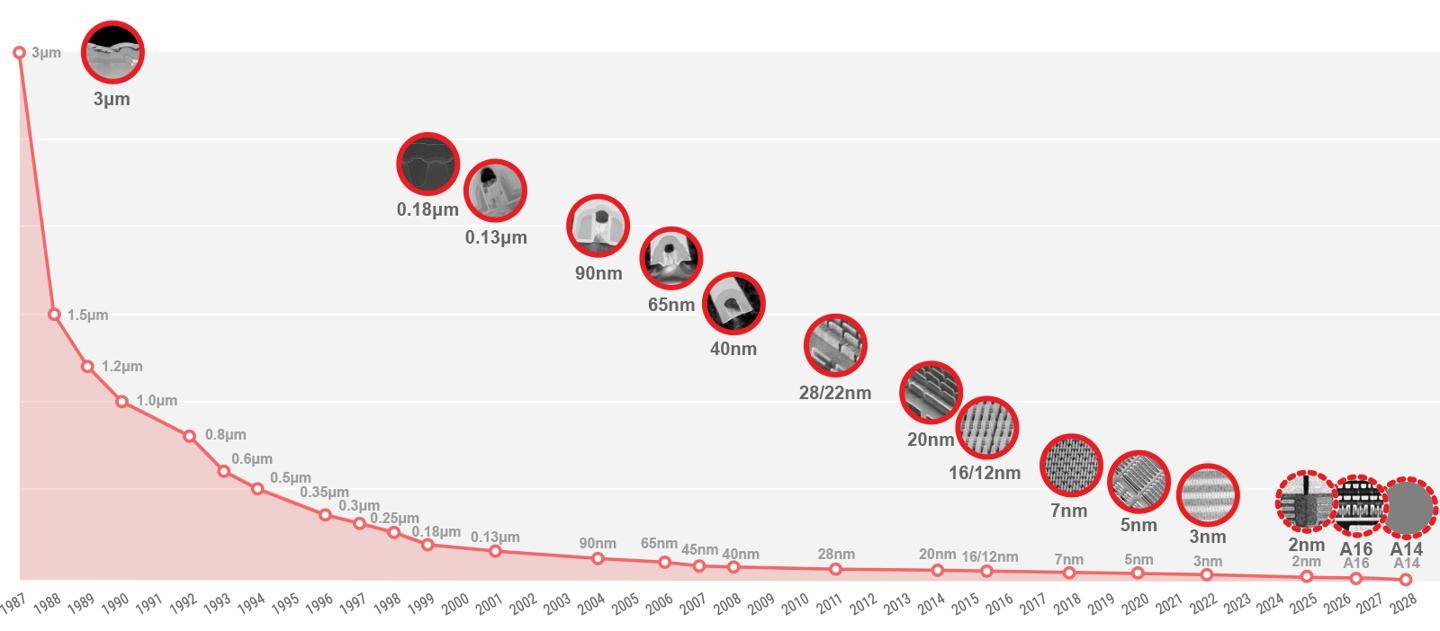

据供应链消息,台积电首个采用背面供电技术(BSPDN)的先进制程节点A16,或将由英伟达率先引入其芯片制造流程。这一决策打破了英伟达自2004年以来沿用台积电最先进制程的"传统",当时其110nm工艺的NV43芯片曾引领行业。

台积电在A16制程中引入的"超级电轨"(Super Power Rail, SPR)技术,通过将供电线路转移至晶圆背面,显著优化了芯片设计空间。该方案不仅解决了传统正面供电带来的压降问题,还维持了与现有工艺相当的栅极密度、布局框架尺寸及元件宽度调节灵活性,为高性能计算芯片提供了更优的物理实现方案。

与台积电第二代2nm工艺N2P相比,A16制程在相同电压下可实现8-10%的性能提升,或在同等性能下降低15-20%的功耗,同时芯片密度提升10%。这种全面的功耗、性能、面积(PPA)优化,使其成为人工智能(AI)和高性能计算(HPC)领域的理想选择。

近年来,台积电先进制程的首发产品多集中于移动处理器和加密货币矿机芯片。不过,这一格局在N2节点被AMD打破——其"Zen 6"架构的EPYC"Venice"处理器成为首个采用该制程的HPC芯片。据行业分析,英伟达计划基于A16制程开发"Rubin"架构之后的下一代AI GPU"Feynman",进一步巩固其在AI加速领域的领先地位。